| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

- Energy Band

- 과잉 캐리어

- 물리전자

- Fermi Energy Level

- Diffusion Current

- KANC

- 나노분석평가

- 서울 경찰서 위도/경도

- 확산 전류

- Scattering

- Charge Carriers

- 앰비폴러 전송 방정식

- 에너지밴드

- 페르미 에너지 준위

- Semiconductor

- 생성(Generation)

- 파동 함수

- 반도체공학

- 캐리어 농도

- Ambipolar transport equation

- Mobility

- 한국나노기술원

- 서울 자치구별 경찰서

- neamen

- Wave Function

- Excess Carrier

- 재결합(Recombination)

- 유효질량

- Density Of states function

- Drift Current

- Today

- Total

읽고 기록하는 삶

[물리전자] 4.1.1 평형 상태일 때의 전자와 정공의 분포(Equilibrium Distribution of Electrons and Holes) 본문

[물리전자] 4.1.1 평형 상태일 때의 전자와 정공의 분포(Equilibrium Distribution of Electrons and Holes)

늦더라도 확실하게 2022. 11. 17. 12:47CHAPTER 4

The Semiconductor in Equilibrium

들어가며

오늘부터 Chapter 4, The Semiconductor in Equilibrium에 대해서 알아보겠습니다.

이번 챕터에서는 Chapter 3에서 다뤘던 내용을 바탕으로, 평형 상태일 때의 반도체를 다룰 것입니다.

평형 상태(Equilibrium, or Thermal Equilibrium)란 ?

: 전기장, 자기장, 온도 구배와 같은 외부의 힘(external force)이 없는 상태

4.1.1 Equilibrium Distribution of Electrons and Holes

반도체에는 두 종류의 전하 캐리어(Charge Carrier)가 있습니다. 바로 전자(electron)와 정공(hole)이죠.

반도체 내부에서 전도대(Conduction Band)의 전자와 가전자대(Valence Band)의 정공이 전류를 만듭니다.

즉, 반도체의 C-V 특성을 알기 위해선 이러한 캐리어가 얼마나 있고, 어떻게 움직이는지 알아야 합니다.

먼저, 전도대(Conduction Band)의 전자의 농도(Concentration of electrons)부터 알아보겠습니다.

지난 시간에 다뤘듯이, 전자의 분포는 상태 밀도 함수와 전자가 양자 상태를 채울 확률의 곱으로 표현됩니다.

그렇다면 전자의 농도는 어떻게 구할 수 있을까요?

바로 다음 글에서 다루겠지만, 전도대(Conduction Band)의 전체 에너지 구간에서 n(E)를 적분하면 됩니다.

가전자대(Valence Band)의 정공의 농도도 유사한 방법으로 구할 수 있습니다.

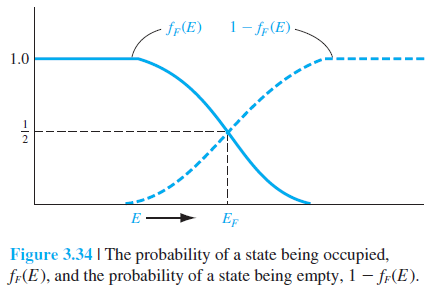

정공의 분포는 상태 밀도 함수와 양자 상태가 비워져 있을 확률의 곱으로 표현됩니다.

즉, 전자가 존재할 확률 함수가 fF(E)이므로, 양자 상태가 비워져 있을 확률은 1-fF(E)입니다.

마찬가지로 정공의 농도는 가전자대(Valence Band)의 전체 에너지 구간에서 p(E)를 적분하면 됩니다.

전자(electron)와 정공(hole)의 농도 그래프를 살펴보기 전에 앞서 다뤘던 내용을 잠깐 복습하고 갈까요?

Figure 3.27은 상태 밀도 함수(Density of States Function), Figure 3.34는 확률 함수(Fermi-Dirac Function) 입니다.

에너지 축을 일치시키고 각각의 그래프를 표현하면 Figure 4.1a와 같이 캐리어의 농도를 시각적으로 알 수 있습니다.

아래의 그림이 전자(electron)와 정공(hole)의 농도를 시각적으로 나타낸 그래프 입니다.

Figure 4.1a의 그래프를 살펴보면 아름답게 대칭을 이루고 있는 것을 확인할 수 있는데요,

이는 몇 가지 조건을 가정하여 가장 이상적으로 나타냈기 때문입니다.

① 진성 반도체(Intrinsic Semiconductor)로 가정

② 전자(electron)와 정공(hole)의 유효질량 동일하다고 가정

③ 페르미 에너지(Fermi Energy)는 Ec 와 Ev의 중간(halfway)에 위치했다고 가정

따라서, 유효 질량이 서로 다르고, Fermi Energy가 변화하게 되면 그래프의 모양이 달라지게 됩니다.

이에 대한 내용은 추후 불순물 반도체(Extrinsic Semiconductor)에서 다루도록 하겠습니다.

한편, Figure 4.1b의 그래프는 Figure 4.1a의 그래프를 확대한 것을 나타낸 것을 의미합니다.

이를 통해 전자(electron)와 정공(hole)의 농도가 어떤 파라미터의 곱으로 형성되는지 확인할 수 있습니다.

마치며

오늘은 반도체에서 전류를 형성하는 캐리어의 농도에 대해 정성적으로 알아보았습니다.

다음 글에서는 해당 개념에 대해 수학적으로 조금 더 공부해보겠습니다.

감사합니다.

'Semiconductor > Device Physics' 카테고리의 다른 글

| [물리전자] 4.1.3 진성 캐리어 농도 (The Intrinsic Carrier Concentration) (0) | 2022.11.23 |

|---|---|

| [물리전자] 4.1.2 평형 상태일 때의 전자와 정공의 농도(The n₀ and p₀ Equations) (0) | 2022.11.18 |

| [물리전자] 3.5.3 페르미-디락 확률 함수 Ⅱ(The Fermi-Dirac Probability Function) (0) | 2022.11.16 |

| [물리전자] 3.5.2 페르미-디락 확률 함수(The Fermi-Dirac Probability Function) (0) | 2022.11.14 |

| [물리전자] 3.4.2 상태 밀도 함수(Density Of States Function) Ⅱ (0) | 2022.11.08 |